https://github.com/flinner/pacmanfpga

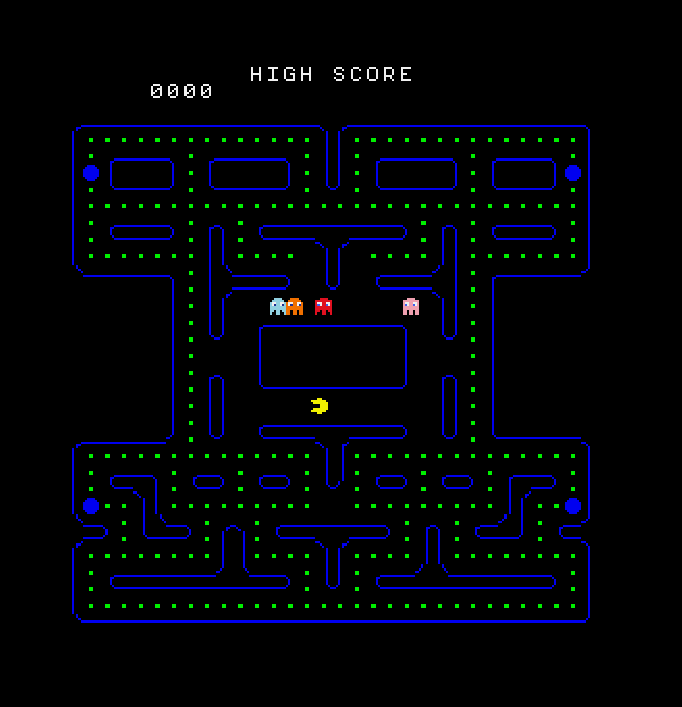

Classic Pacman Implementation on a Xilinx FPGA! Simulated with Verilator + SFML

https://github.com/flinner/pacmanfpga

fpga game pacman sfml verilator vivado xilinx

Last synced: 4 months ago

JSON representation

Classic Pacman Implementation on a Xilinx FPGA! Simulated with Verilator + SFML

- Host: GitHub

- URL: https://github.com/flinner/pacmanfpga

- Owner: Flinner

- License: cern-ohl-s-2.0

- Created: 2024-11-02T08:21:53.000Z (11 months ago)

- Default Branch: main

- Last Pushed: 2024-12-06T12:03:43.000Z (10 months ago)

- Last Synced: 2025-02-13T17:54:16.851Z (8 months ago)

- Topics: fpga, game, pacman, sfml, verilator, vivado, xilinx

- Language: SystemVerilog

- Homepage: https://ammar.engineer/posts/2024/12/04/pacman-on-an-fpga-in-systemverilog/

- Size: 12.1 MB

- Stars: 2

- Watchers: 2

- Forks: 1

- Open Issues: 0

-

Metadata Files:

- Readme: README.md

Awesome Lists containing this project

README

# Simulation

To Run VGA simulator (VERY SLOW, around 0.3 frames/second!):

```bash

cmake -B build -G Ninja

ninja -C build

# Run it

./build/Vour

```

# Synthesis

To generate bitstream:

1. Launch Vivado (Yikes!)

2. Select Tools Menu

3. Run TCL Scripts

4. Navigate to cloned repo, Run `Pacman.tcl`

5. Write Bitstream

# Scripts

## Generate `font.sv` from `.ttf`:

```bash

python scripts/ttf_to_sv.py > rtl/ip/font.sv

```

## Generate `.mem` for audio.wav:

```bash

# It will overwite the .mem files

python scripts/convert_wav_to_mem.py

```

# Format All code:

```bash

find . -name "*.sv" -exec verible-verilog-format --inplace {} \;

```